- Ejemplo 1.- Encender los 8 leds en forma secuencial activando PLL utilizando IP CORE PLL xilinx 14.7(Clocking Wizard). La máxima frecuencia de este core es 600 Mhz

- Las herramientas necesarias para realizar estos ejemplos son:

Ø Xilinx vivado 2013.4

Ø DK Desing suite 5.0 SP5

Ø Tarjeta Zedboard (XC7Z020)

Ø CORE Generator 14.7

- PASO 1.

Utilizar CORE Generator de xilinx

14.7(Clocking Wizard) para obtener el IP CORE de un PLL corriendo a 600 Mhz

llamado clk_wiz_v3_6.vhd. Las

configuraciones son las siguientes:

·

Primitive: PLLE2_ADV

·

CLK_OUT1 = 600 Mhz

·

Option

Input/Output = deshabilitadas RESET, LOCKED y POWER_DOWN

Estructura de archivos

- PASO 2.

Hacer un nuevo

proyecto en DK Handel-C llamado LED. El código de main.hcc es el siguiente:

#include

"delay.hch"

#define C_MHZ 600

signal unsigned 1 x=1;

set reset = internal

!x; // resets when x is zero

interface bus_in (unsigned 1 pin) clock_pin () with {data = {"CLK"}}; // Pin Y9 del reloj de 100 Mhz

// tienes que poner en el archivo

main_hcc.vhd --> I0_clk_wiz_v3_6_main_34 : entity work.clk_wiz_v3_6

interface clk_wiz_v3_6(unsigned 1 CLK_OUT1)

clk_wiz_v3_6(unsigned 1 CLK_IN1 =clock_pin.pin) with {busformat="B<I>"}; // le pasas los 100 Mhz

set clock = internal

clk_wiz_v3_6.CLK_OUT1; // recibes los 600

Mhz

unsigned 1 P_LedStatus;

unsigned 8 LEDS;

interface bus_out() salida(LEDS) with {data =

{"LD7","LD6","LD5","LD4","LD3","LD2","LD1","LD0"}};

void main(void)

{

par

{

while(1)

{

LEDS++;

delay_ms(C_MHZ,1000); // esperas 1000 ms

}

}

}

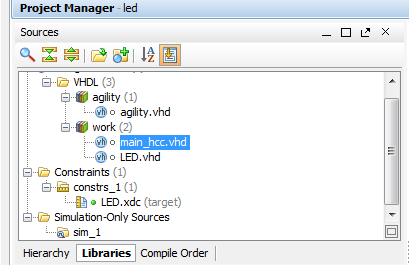

- PASO 3.

Hacer un proyecto en Vivado de Xilinx

llamado LED y agregar los archivos clk_wiz_v3_6.vhd, main_hcc.vhd, agility.vhd,

LED.vhd.

- PASO 4.

Crear un archivo

constraint llamado LED.xdc con el siguiente código:

set_property PACKAGE_PIN Y9 [get_ports {PIN_CLK}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_CLK}]

set_property PACKAGE_PIN T22 [get_ports {PIN_LD0}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD0}]

set_property PACKAGE_PIN T21 [get_ports {PIN_LD1}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD1}]

set_property PACKAGE_PIN U22

[get_ports {PIN_LD2}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD2}]

set_property PACKAGE_PIN U21 [get_ports {PIN_LD3}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD3}]

set_property PACKAGE_PIN V22 [get_ports {PIN_LD4}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD4}]

set_property PACKAGE_PIN W22 [get_ports

{PIN_LD5}]

set_property IOSTANDARD LVCMOS33 [get_ports

{PIN_LD5}]

set_property PACKAGE_PIN U19 [get_ports {PIN_LD6}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD6}]

set_property PACKAGE_PIN U14 [get_ports {PIN_LD7}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD7}]

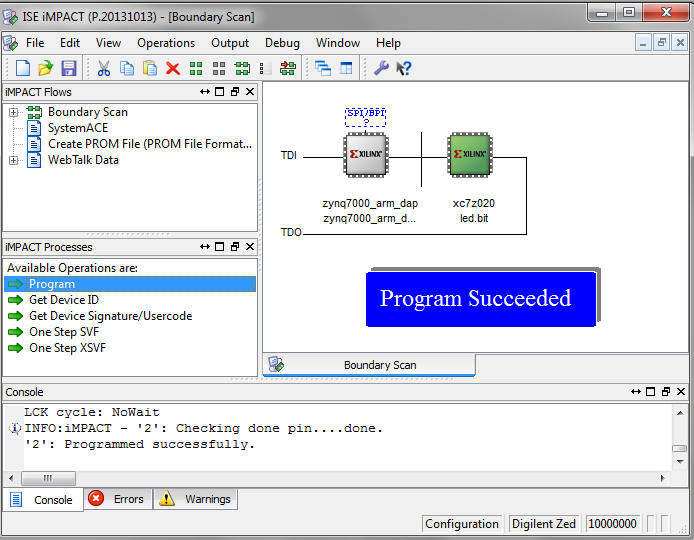

- PASO 5.

Cambiar en la línea 164 del archivo

main_hcc.vhd I0_clk_wiz_v3_6_main_9 :

clk_wiz_v3_6 por I0_clk_wiz_v3_6_main_

: entity work. clk_wiz_v3_6.

Después guardar e implementar todo el proceso y obtener el Bitstream LED.bit

- Ejemplo 2.- Encender los 8 leds en forma secuencial activando PLL utilizando IP catalog de xilinx vivado 2013.4. La máxima frecuencia de este core es 600 Mhz

Las herramientas necesarias para realizar estos ejemplos son:

Ø Xilinx vivado 2013.4

Ø DK Desing suite 5.0 SP5

Ø Tarjeta Zedboard (XC7Z020)

- PASO 1.

Hacer un nuevo

proyecto en DK Handel-C llamado LED. El código de main.hcc es el siguiente:

#include

"delay.hch"

#define C_MHZ 600

signal unsigned 1 x=1;

set reset = internal

!x; // resets when x is zero

interface bus_in (unsigned 1 pin) clock_pin () with {data = {"CLK"}}; // Pin Y9 del reloj de 100 Mhz

interface clk_pll_750Mhz (unsigned 1 CLK_OUT1)

clk_pll_750Mhz (unsigned 1 CLK_IN1 =clock_pin.pin) with {busformat="B<I>"}; // le pasas los 100 Mhz

set clock = internal

clk_pll_750Mhz.CLK_OUT1; // recibes los 600

Mhz

unsigned 1 P_LedStatus;

unsigned 8 LEDS;

interface bus_out() salida(LEDS) with {data =

{"LD7","LD6","LD5","LD4","LD3","LD2","LD1","LD0"}};

void main(void)

{

par

{

while(1)

{

LEDS++;

delay_ms(C_MHZ,1000); // esperas 1000 ms

}

}

}

- PASO 2.

Hacer un proyecto en Vivado de Xilinx

llamado LED y agregar los archivos main_hcc.vhd, agility.vhd, LED.vhd.

- PASO 3.

Crear un archivo

constraint llamado LED.xdc con el siguiente código:

set_property PACKAGE_PIN Y9 [get_ports {PIN_CLK}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_CLK}]

set_property PACKAGE_PIN T22 [get_ports {PIN_LD0}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD0}]

set_property PACKAGE_PIN T21 [get_ports {PIN_LD1}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD1}]

set_property PACKAGE_PIN U22

[get_ports {PIN_LD2}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD2}]

set_property PACKAGE_PIN U21 [get_ports {PIN_LD3}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD3}]

set_property PACKAGE_PIN V22 [get_ports {PIN_LD4}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD4}]

set_property PACKAGE_PIN W22 [get_ports

{PIN_LD5}]

set_property IOSTANDARD LVCMOS33 [get_ports

{PIN_LD5}]

set_property PACKAGE_PIN U19 [get_ports {PIN_LD6}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD6}]

set_property PACKAGE_PIN U14 [get_ports {PIN_LD7}]

set_property IOSTANDARD LVCMOS33 [get_ports {PIN_LD7}]

- PASO 4.

Hacer

clic en IP Catalog de la parte de la pestaña de Project Manager de vivado y

escribir Clocking Wizard, después hacer doble clic en esa opción.

- Especificar las siguientes características del IP core:

·

Componet Name: clk_pll_750Mhz

(se quedó con ese nombre porque en vivado 2013.4 si corria con 750 mhz)

·

Clocking Options: primitive àPLL

·

Output

Clocks: Output Freq (mhz) à600.000. Enable options

Input/Outputs à deshabilitar

reset y locked.

Hacer

clic en OK y después en la ventana que aparece hacer clic en generate.

Después

guardar e implementar todo el proceso y obtener el Bitstream LED.bit

No hay comentarios.:

Publicar un comentario